Which can also be found in the timing diagrams of the Memory Usage Guide for the iCE40 Devices. Ports are registered at the input of the memory array. In all the sysMEM RAM modes, the input data and addresses for the That said, you should be able to write a simple behavioral model for easy cases such as this, as long as you follow the datasheet for the iCE40 family, which says clearly: In general, if things keep on not working, open the documentation and follow the synthesis style guide which will show you the exact VHDL/verilog you need to write to infer your favorite blockRAM. Reason for this is that one of the process is quite more complex, so it's harder to turn it into a computational process involving "next" signals. I did not try this for both buffers simultaneously but only one of them. Unfortunately, despite the added complexity (and decreased readability) in the code, the results were still the same, unable to map to RAM instance. a sh*tload of similar statement involving "next" signals

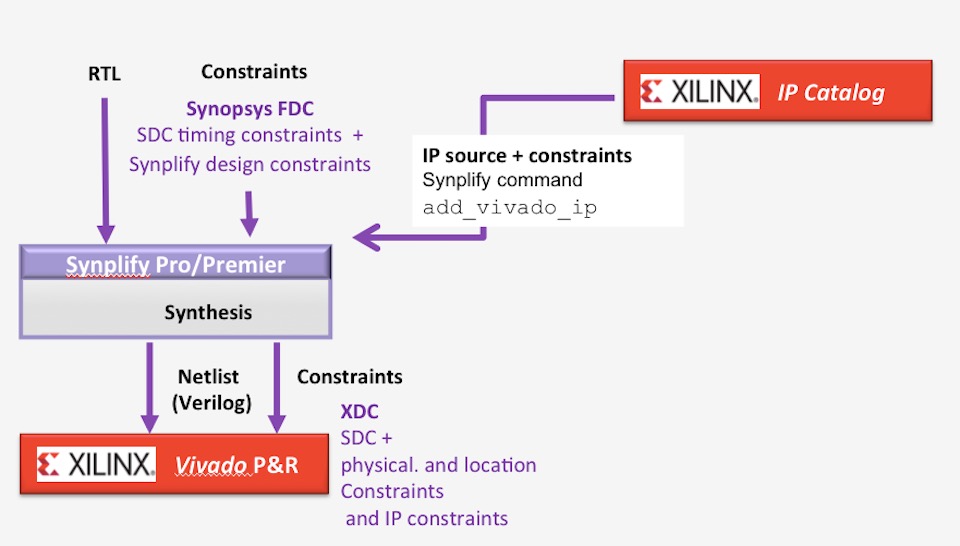

#Synplicity synplify pro update

Explicit update to registers for logic described in above thread Received_message_data <= received_message(received_message_adr)

Process(received_message, received_message_adr) Explicit asynchronous SRAM read for above thread The first method is made of synchronous processes.

#Synplicity synplify pro code

This is not per-se catastrophic as the design can still work, but it is very wasteful of FPGA ressources and makes routing long and difficult.ĮDIT : As for how the registers themselves are accessed, the code is actually quite complex and long so it'd be pointless to post it entirely here.

The problem is that it doesn't tell me at all WHY it's unable to map RAM instance. FX703 :"d:\.vhd":196:8:196:20|Unable to map RAM instance reply_message to RAM for technology FX703 :"d:\.vhd":189:8:189:23|Unable to map RAM instance received_message_1 to RAM for technology FX703 :"d:\.vhd":189:8:189:23|Unable to map RAM instance received_message to RAM for technology MF135 :"d:\.vhd":196:8:196:20|RAM reply_message (in view: work.test_bitbus(behavioral)) is 32 words by 8 MF135 :"d:\.vhd":189:8:189:23|RAM received_message_1 (in view: work.test_bitbus(behavioral)) is 32 words by 8 MF135 :"d:\.vhd":189:8:189:23|RAM received_message (in view: work.test_bitbus(behavioral)) is 32 words by 8 MF794 |RAM received_message required 768 registers during mapping Make sure that there are no unused intermediate registers.Īnd finally it renounces using the hardware block RAMs but uses registers to simulate it instead. I get a ton of messages such as CL169 :"C:\lscc\iCEcube2.2017.08\synpbase\lib\vhd\std.vhd":1:1:1:2|Pruning unused register received_message_31(7 downto 0). That's great ! However just after it seems to remove some redundancy.

There's a mechanism normally preventing reading and writing from the same buffer at the same time. The idea is that one process recieves messages, while the other sends replies. They are then accessed in two separate process, one process writes to buffer A and reads from buffer B, and the other process does the oposite. The type of the buffers is as follow : type MESSAGE_T is array(0 to 31) of std_logic_vector(7 downto 0) I have a design on an iCE40 FPGA, I use iCEcube2 to compile the VHDL code and in my design I try to infer two small RAM buffers.

0 kommentar(er)

0 kommentar(er)